[AK2572]

## AKM

# AK2572

APC for Burst Mode Applicable Direct Modulation Laser Diode

#### FEATURES

■ Temperature compensation programming function (APC\_FF) of Bias current (0~85mA) and Modulation current (0~10mA/0~2.2V) responding to the detected temperature by the On-chip temperature sensor.

- Stable feedback function in the digital scheme (APC FB).

- ■SFP support TXFAULT function and 1k bit ID field (EEPROM User Area).

- ■LD Power leveling function by either Hardware pin control or Register setting.

■Various alarm functions of Optical output decline (OPTALM), Excessive LD current (CURRALM), Exceptional temperature (TEMPALM) and Irregular external signals (EXTALM1 and EXTALM2).

■ Operation adjustment function via 2-wire Digital interface after assembled into sub-system.

On-chip Oscillator allows a Self-running operation.

■ Single 3.3 V [Typ.] power supply.

## APPLICATIONS

For LD modules applied to Continuous and Burst mode

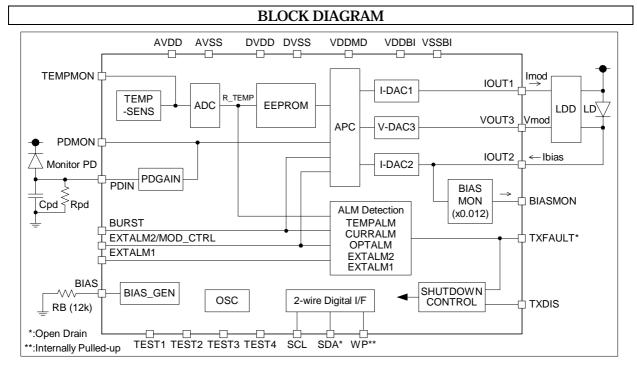

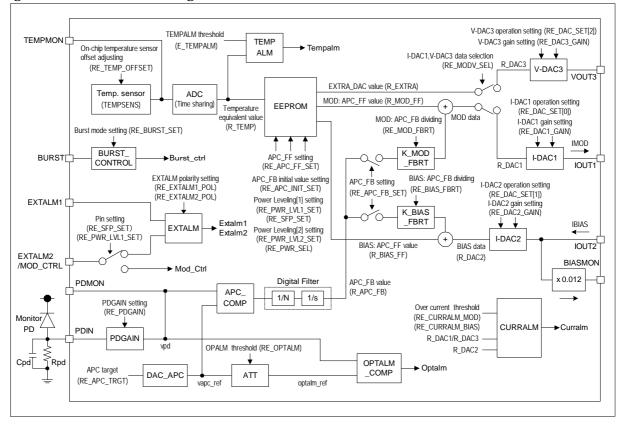

The AK2572 enables to keep the optical power of the direct modulation LD (Laser Diode) constant by the APC (Automatic Power Control) circuit. It consists of a current programming function (APC\_FF) responding to the temperature characteristics of each LD, and a Digital feedback function (APC\_FB) to adjust the LD current

OUTLINES

based on the monitoring PD (Photo Diode) current. The AK2572 is also applicable to the Burst mode transmission. The device equips a Power leveling function to switch a temperature compensation programming data by either Hardware pin control or Register setting.

The On-chip EEPROM (Non-volatile memory) allows to adjust and to keep the individual setting data for each LD characteristics via 2-wire Digital interface after being assembled into sub-system. As 1k bits User Area is allocated in the EEPROM, which supports the ID field of the SFP specification, a proper operation required for the SFP module is realized by using the TXFAULT function.

## ORDERING GUIDE

| Product Number | Package Type               |

|----------------|----------------------------|

| AK2572         | <b>QFN28</b> (5.2mm×5.2mm) |

## = Table of Contents =

| I.   | PIN DESCRIPTION ====================================                  | - <b>4</b> |

|------|-----------------------------------------------------------------------|------------|

| II.  | ABSOLUTE MAXIMUM RATINGS ====================================         | 6          |

| III. | RECOMMENDED OPERATING CONDITIONS ==================================== | - 6        |

| IV.  | ELECTRICAL CHARACTERISTICS ====================================       | = <b>6</b> |

|      | (1) Current Consumption                                               | 3          |

|      | (2) EEPROM Characteristics                                            |            |

|      | (3) Digital Input / Output Pin DC Characteristics                     | 3          |

|      | (4) Digital Input / Output Pin AC Characteristics                     | 1          |

|      | (5) I-DAC1 Characteristics                                            |            |

|      | (6) I-DAC2 Characteristics                                            |            |

|      | (7) V-DAC3 Characteristics                                            |            |

|      | (8) Current Monitor (BIASMON)                                         |            |

|      | (9) PDGAIN                                                            |            |

|      | (10) DAC_APC                                                          |            |

|      | (11) BIASGEN                                                          |            |

|      | (12) Temperature Serisor (13) ADC                                     |            |

|      | (13) ADC (14) Power On Reset                                          |            |

|      | (15) On-chip Oscillator                                               |            |

|      | (16) OPTALM                                                           |            |

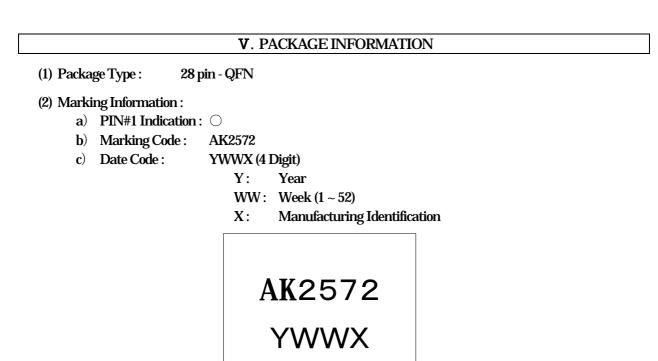

| V.   | PACKAGE INFORMATION ====================================              |            |

|      | (1) Package Type                                                      |            |

|      | (2) Marking Information                                               |            |

|      | (3) Package Outline Dimension                                         |            |

| VI.  | CIRCUIT DESCRIPTION ====================================              |            |

|      | 1. Operational Description Notation                                   | 1          |

|      | 2. Operation Setting                                                  |            |

|      | 3. I-DAC, V-DAC Functional Part                                       |            |

|      | 4. APC Functional Part                                                |            |

|      | 4.1 APC_FF Function                                                   | 4          |

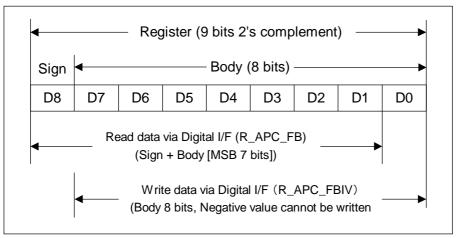

|      | 4.2 APC_FB Function                                                   |            |

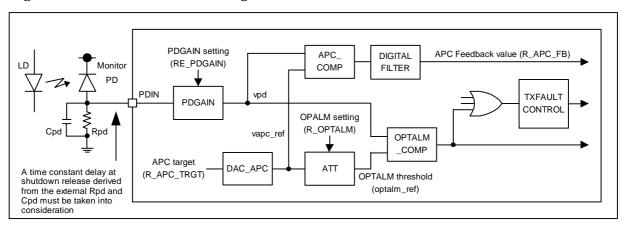

|      | 4.2.1 APC_FB Circuit Block Diagram                                    | 6          |

|      | 4.2.2 Normalization of PD Monitoring Current                          |            |

|      | 4.2.3 DAC_APC                                                         |            |

|      | 4.2.4 APC_FB Dividing Function                                        |            |

|      | 4.3 APC Operation Setting                                             |            |

|      | 4.4 On-Chip Temperature Sensor (TEMPSENS) Characteristics             |            |

|      | 4.5 Current Monitor         5. Burst Mode Operation                   |            |

|      | 5. Burst Mode Operation                                               |            |

|      | 5.2 Power Leveling [2]2                                               |            |

|      |                                                                       |            |

| 6.      | Alarm Function                                                    | 27      |

|---------|-------------------------------------------------------------------|---------|

|         | 6.1 TEMPALM                                                       | 27      |

|         | 6.2 OPTALM                                                        | 27      |

|         | 6.3 CURRALM                                                       | 27      |

|         | 6.4 EXTALM1, EXTALM2                                              | 27      |

|         | 6.5 TXFAULT                                                       | 28      |

|         | 6.5.1 Target Alarm Setting of TXFAULT Output                      | 28      |

|         | 6.5.2 Operation at TXFAULT Detection                              |         |

| 7.      | Shutdown Control                                                  | 29      |

|         | 7.1 Shutdown Operation                                            | 29      |

|         | 7.2 Operation at Shutdown Release                                 | 29      |

| 8.      | Start-Up Setting in SFP Support Mode                              | 30      |

|         | 8.1 TXFAULT Detection at Power-Up and after Release from Shutdown |         |

|         | 8.1.1 OPTALM                                                      | 30      |

|         | 8.1.2 EXTALM1, EXTALM2                                            | 30      |

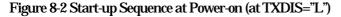

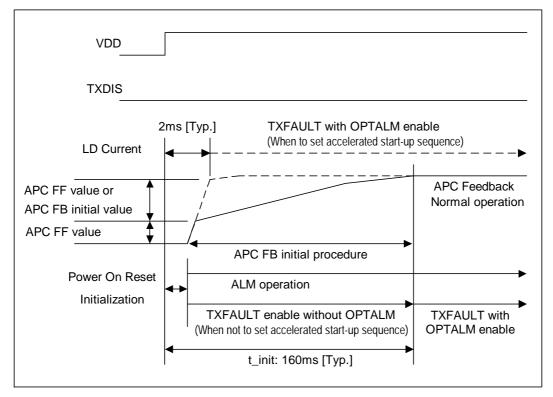

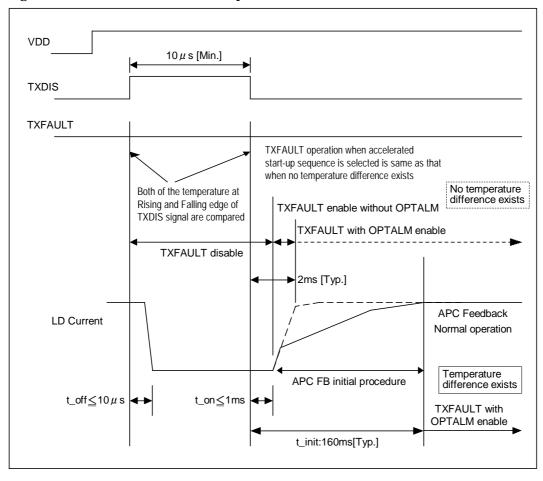

|         | 8.2 At Power-On (at TXDIS="L")                                    | 31      |

|         | 8.3 At Power-On (at TXDIS="H")                                    | 31      |

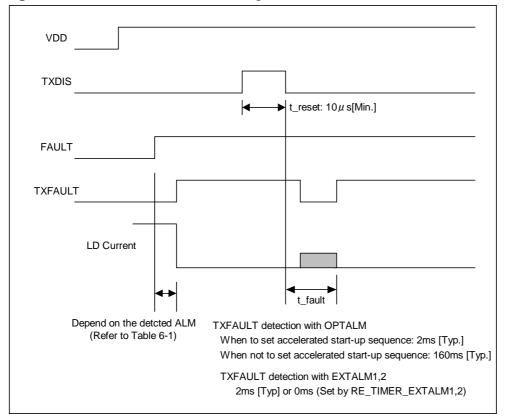

|         | 8.4 At TXDIS Detection / Release                                  | 32      |

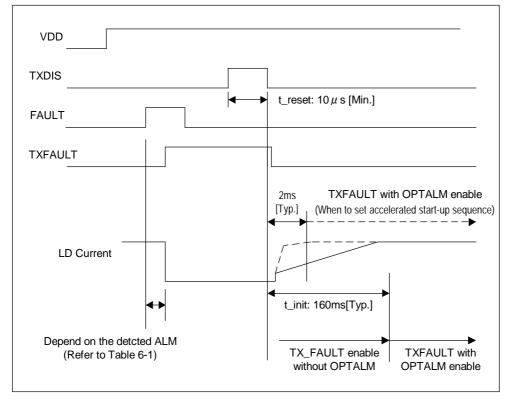

|         | 8.5 At TXFAULT Detection / Release                                | 33      |

| 9.      | Digital Interface Configuration                                   | 34      |

|         | 9.1 Memory Configuration                                          |         |

|         | 9.2 Write Protect Operation                                       |         |

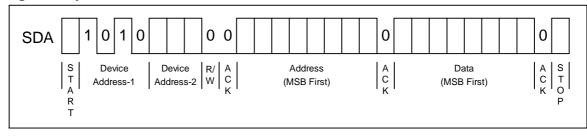

|         | 9.3 Read / Write Operation                                        | 36      |

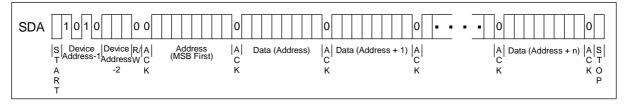

|         | 9.3.1 Byte Write                                                  | 36      |

|         | 9.3.2 Page Write                                                  | 36      |

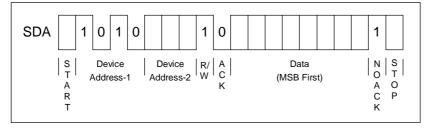

|         | 9.3.3 Current Address Read                                        | 36      |

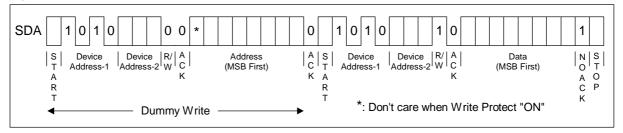

|         | 9.3.4 Random Read                                                 | 36      |

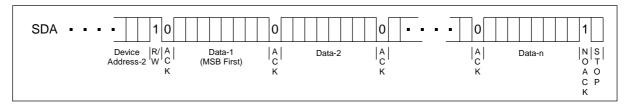

|         | 9.3.5 Sequential Read                                             | 37      |

|         | 9.3.6 Data Change                                                 | 37      |

|         | 9.3.7 Start/Stop                                                  | 37      |

|         | 9.4 EEPROM Configuration                                          | 38      |

|         | 9.5 Register Configuration                                        | 40      |

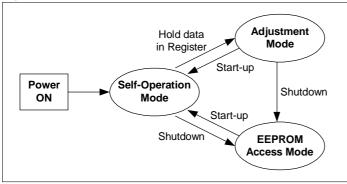

| 10.     | . Operation Modes                                                 | 44      |

|         | 10.1 Self-Operation Mode                                          | 44      |

|         | 10.2 Adjustment Mode                                              | 44      |

|         | 10.3 EEPROM Access Mode                                           | 44      |

|         | 10.4 Mode Control                                                 | 44      |

|         | 10.5 Operation Mode Change Commands                               | 45      |

|         | 10.6 Mode Protection                                              | 45      |

| 11.     | Example of Adjusting Sequence                                     | 46      |

| VII. EX | XTERNAL CIRCUIT EXAMPLE ====================================      | ==== 47 |

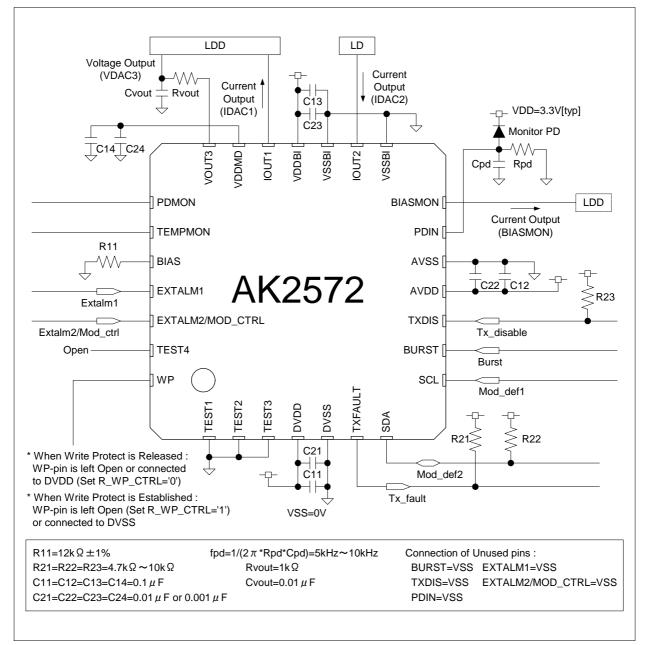

#### I. PIN DESCRIPTION

Each symbol at I/ O column in the following table means,

PWR: Power (VDD) or VSS, Ai: Analog input, Ao: Analog output,

Di : Digital input, Di\_pu : Digital input with pulled-up resistor,

Do : Digital output, Do\_od : Digital output (Open drain), Dio\_od : Digital input/output (Open drain)

| Pin#   | Pin Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I/O    | Note                                   |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|

| 1      | TEST1    | Input pin for AKM test. Connect it to DVSS for Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Di     |                                        |

| 2      | TEST2    | Input pin for AKM test. Connect it to DVSS for Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Di     | Connect it                             |

| ~<br>3 | TEST3    | Input pin for AKM test. Connect it to DVSS for Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Di     | to DVSS                                |

| 4      | DVDD     | Power supply for Digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PWR    |                                        |

| 5      | DVSS     | Ground for Digital circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PWR    |                                        |

| 6      | TXFAULT  | Alarms such as Optical output decline (OPTALM), Excessive LD current (CURRALM), Exceptional temperature (TEMPALM) and Irregular external signals (EXTALM1 and EXTALM2) can be selected by EEPROM / Register setting as target alarms available on TXFAULT-pin output.<br>When any of the selected alarms (ALM) is detected, TXFAULT-pin becomes "High-Z" output, and it becomes "H" level with a pulled-up resistor connection. This pin is open-drain type and should be connected to DVDD via a $4.7k \sim 10k \Omega$ resistor.<br>With RE_SFP_SET="0" (SFP support mode setting), TXFAULT-pin output is held at "H" level when any of the selected alarms is detected till the shutdown request is released by "H" to "L" transition on TXDIS-pin. | Do_od  | Connect it<br>to Pulled-up<br>resistor |

| 7      | SDA      | Serial data input / output pin for Digital interface.<br>This pin is open-drain type and should be connected to DVDD via a $4.7k \sim 10k \Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Dio_od | Connect it<br>to Pulled-up<br>resistor |

| 8      | SCL      | Serial clock input for Digital interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Di     | Should not<br>be left open             |

| 9      | BURST    | Burst signal input. It is active during "H" input period (valid data period). When this pin is not used, connect it to DVSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Di     | Should not<br>be left open             |

| 10     | TXDIS    | When this pin is at "H" input, Bias current DAC (I-DAC2) output<br>and Modulation current DAC (I-DAC1 or V-DAC3) output are<br>disabled. Refer to Table 7-1 and Table 7-2.<br>At RE_SFP_SET="0" (SFP support mode setting), a logical sum of<br>TXFAULT output and TXDIS-pin input become a disable request.<br>At RE_SFP_SET="1", TXDIS-pin input becomes a disable request.<br>When this pin is externally pulled-up, use a higher than $4.7k\Omega$<br>resistor. When this pin is not used, connect it to DVSS.                                                                                                                                                                                                                                     | Di     | Should not<br>be left open             |

| 11     | AVDD     | Power supply for Analog circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PWR    |                                        |

| 12     | AVSS     | Ground for Analog circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PWR    |                                        |

| 13     | PDIN     | Monitoring PD (Photo Diode) voltage input.<br>The detected monitor PD current is I to V converted by external resistor and capacitor. Please adjust the cut-off frequency of an LPF to be within $5k \sim 10$ kHz which is composed of external resistor (Rpd) and capacitor (Cpd).<br>When this pin is not used, it is recommended to connect it to AVSS.                                                                                                                                                                                                                                                                                                                                                                                             | Ai     |                                        |

| 14     | BIASMON  | Bias current monitor. A current multiplied by 0.012 [Typ.] of the I-DAC2 output current is sourced from this pin. When to convert the current to a voltage by an external resistor, select the resistor value such that BIASMON-pin voltage $\leq 1.3$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ao     |                                        |

| 15     | VSSBI    | Ground for I-DAC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PWR    |                                        |

## Pin Description (Continued)

| Pin#   | Pin Name    | Function                                                                                                                       | I/O   | Note                       |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|

| 1 11// | 1 III vante | LD Bias current output (Current-sink type : Maximum sink current                                                               | 10    | THOLE                      |

|        |             | = 85.0 mA [Typ.]). The current value is set by I-DAC2.                                                                         |       |                            |

| 16     | IOUT2       | Please operate the device under IOUT2-pin voltage $\geq$ (VDD-1.7 V)                                                           | Ao    |                            |

| 10     | 10012       | condition. When the voltage on this pin becomes lower, a sink                                                                  | ΠŪ    |                            |

|        |             | current error becomes larger.                                                                                                  |       |                            |

| 17     | VSSBI       | Ground for I-DAC2                                                                                                              | PWR   |                            |

| 18     | VDDBI       | Power supply for I-DAC2.                                                                                                       | PWR   |                            |

|        |             | I-DAC1 current output (Current-source type : Maximum sourcing                                                                  |       |                            |

|        |             | current 10.2 mA [Typ.]).                                                                                                       |       |                            |

|        |             | When $RE_MODV_SEL = "0"$ , this becomes an LD modulation                                                                       |       |                            |

| 10     |             | current output and when $RE_MODV_SEL = "1"$ , it is I to V                                                                     |       |                            |

| 19     | IOUT1       | converted and it can be used as an APD control voltage or a                                                                    | Ao    |                            |

|        |             | reference voltage for LDD (Laser Diode Driver) etc Please operate                                                              |       |                            |

|        |             | the device under IOUT1-pin voltage $\leq 1.3$ V. When the voltage on                                                           |       |                            |

|        |             | this pin becomes higher, a sourcing current error becomes larger.                                                              |       |                            |

| 20     | VDDMD       | Power supply for I-DAC1.                                                                                                       | PWR   |                            |

|        |             | V-DAC3 voltage output pin (Maximum output voltage: 2.2 V [Typ.]).                                                              |       |                            |

|        |             | When RE_MODV_SEL="0", this voltage can be used as either an                                                                    |       | Connect it to              |

| 21     | VOUT3       | APD control voltage or LDD reference voltage etc When                                                                          | Ao    | Connect it to external RC  |

| ~1     | V0013       | $RE_MODV_SEL = "1"$ , this outputs an LD modulation current                                                                    | AU    | filter                     |

|        |             | control voltage. Please connect an external RC filter (LPF : R=1k $\Omega$                                                     |       | inter                      |

|        |             | and C=0.01 $\mu$ F are recommended) to this pin.                                                                               |       |                            |

|        |             | PDMON is the Normalized PDIN voltage output pin.                                                                               |       |                            |

| 22     | PDMON       | Adjust RE_PDGAIN so that PDMON voltage is equal to 1.0 V [typ].                                                                | Ao    |                            |

| ~~     |             | When APC_FB function or OPTALM function is used,                                                                               |       |                            |

|        |             | RE_PDGAIN adjustment is required.                                                                                              | •     |                            |

| 23     | TEMPMON     | On-chip temperature sensor voltage output.                                                                                     | Ao    | 0                          |

| 24     | BIAS        | BIAS resistor connection pin.                                                                                                  | Ao    | Connect it to              |

|        |             | Connect this pin to AVSS via a $12k \Omega \pm 1\%$ resistor.<br>Irregular external signal detect [1] input pin. A polarity of |       | a resistor                 |

|        |             | EXTALM1 detection can be selected by RE_EXTALM1_POL.                                                                           |       | Should not                 |

| 25     | EXTALM1     | EXTALM detection can be selected by KE_EXTALM_FOL.<br>EXTALM can be set as a target TXFAULT output alarm by                    | Di    | be left open               |

|        |             | RE_EXTALM1_SET. When this pin is not used, connect it to DVSS.                                                                 |       | be left open               |

|        |             | This pin functions as MOD_CTRL input pin when both                                                                             |       |                            |

|        |             | RE_SFP_SET="1" and RE_PWR_LVL1_SET="1".                                                                                        |       |                            |

|        |             | This pin becomes EXTALM2 input pin when either RE_SFP_SET                                                                      |       |                            |

|        |             | $= "0" \text{ or } \text{RE}_{PWR} \text{LVL1}_{SET} = "0".$                                                                   |       |                            |

|        |             | When MOD_CTRL-pin function (Power leveling [1] control signal                                                                  |       |                            |

|        | EXTALM2/    | input pin) is selected, Power leveling [1] is executed by a Hardware                                                           |       | Chauld not                 |

| 26     | MOD_CTRL    | pin control. In this case, then, EXTALM2-related function is                                                                   | Di    | Should not<br>be left open |

|        | WOD_CIKL    | automatically turned off.                                                                                                      |       | be left open               |

|        |             | When EXTALM2-pin function (Irregular external signal detection                                                                 |       |                            |

|        |             | [2] input pin) is selected, EXTALM2 is set as a target TXFAULT                                                                 |       |                            |

|        |             | output alarm by RE_EXTALM2_SET, and RE_EXTALM2_POL                                                                             |       |                            |

|        |             | sets the polarity of EXTALM2 detection. When this pin is not used,                                                             |       |                            |

| 07     | TTOTA       | connect it to DVSS.                                                                                                            | P     | 0                          |

| 27     | TEST4       | Output pin for AKM test. Leave it open for Normal operation.                                                                   | Do    | Open                       |

|        |             | Write protect control pin. This pin is internally pulled-up via a $20k\Omega$                                                  |       |                            |

| 28     | WP          | [Typ.] resistor. WP-pin and R_WP_CTRL set the limitation of an                                                                 | Di_pu |                            |

|        |             | accessible EEPROM space via Digital interface. Please refer to Section 9.2 for datails                                         |       |                            |

|        |             | Section 9.2 for details.                                                                                                       |       |                            |

| Item                 | Symbol | Min.    | Max.    | Unit | Note                             |

|----------------------|--------|---------|---------|------|----------------------------------|

| Power Supply Voltage | VDD    | - 0.3   | 6.0     | V    | AVDD, DVDD, VDDMD, VDDBI         |

| Ground Level         | VSS    | 0.0     | 0.0     | V    | AVSS, DVSS, VSSBI (Base Voltage) |

| Input Voltage        | VIN    | VSS-0.3 | VDD+0.3 | V    | Excluding VDD-pins               |

| Input Current        | IIN    | - 10    | 10      | mA   | Excluding VDD-pins               |

| Storage Temperature  | Tstg   | - 55    | 130     | °C   |                                  |

## **I**. ABSOLUTE MAXIMUM RATINGS

## **III. RECOMMENDED OPERATING CONDITIONS**

| Item                          | Symbol | Min. | Тур. | Max. | Unit | Note             |

|-------------------------------|--------|------|------|------|------|------------------|

| Operating Ambient Temperature | Та     | - 40 |      | + 85 | °C   |                  |

| Davion Symphy Voltage         | VDD    | 3.0  | 3.3  | 3.5  | V    | 3.3V (-9% / +6%) |

| Power Supply Voltage          | VSS    | 0.0  | 0.0  | 0.0  | V    | Base Voltage     |

< Important Notice > Please pay attention not to keep the condition of VDD≦1.5V which makes that the Power On Reset function of AK2572 cannot operate correctly, AK2572 supplies the abnormal LD current and the possibility of damaging LD increases.

## IV. ELECTRICAL CHARACTERISTICS

#### (1) Current Consumption

| Item                               | Symbol | Min. | Тур. | Max. | Unit | Note       |

|------------------------------------|--------|------|------|------|------|------------|

| Current Consumption (All VDD-pins) | IDD    | _    | 21   | 26   | mA   | [*1], [*2] |

[\*1] It doesn't include the output current of I-DACs.

[\*2] R\_DACx=FFh (x=1~3), R\_DAC1,2\_GAIN=1, R\_DAC3\_GAIN=0, PDGAIN=0dB, PDIN=1V

(2) EEPROM Characteristics

| Item                       | Min. | Max. | Unit  | Condition                             |  |  |  |  |

|----------------------------|------|------|-------|---------------------------------------|--|--|--|--|

| EEPROM Write Cycle         | 1000 | —    | times | [*]                                   |  |  |  |  |

| EEPROM Data Retention Time | 10   | —    | year  | Junction temperature $Tj=85^{\circ}C$ |  |  |  |  |

|                            |      |      |       |                                       |  |  |  |  |

$\left[*\right]$  This parameter is characterized and is not 100% tested.

< Important Notice > The adjusted data in AKM factory are stored in advance at address location (Device Address=A6h, Address=60h) for the offset voltage of the On-chip temperature sensor. If such excessive temperature stress is to be applied to the AK2572 which exceeds a guaranteed EEPROM data retention conditions (for 10 years at 85°C), it is important to read the pre-determined data in advance and to re-write the same data back into EEPROM after an exposure to the excessive temperature environment. Even if the exposure time is shorter than the retention time, any accelerated temperature stress tests (such as baking) are performed, it is recommended to read the pre-set data first and to re-write it after the test. Access to unused address locations is not functionally guaranteed. Please refer to Section 9.4, "EEPROM Configuration".

| Item                      | Symbol | Min.   | Max. | Unit             | Condition                          |

|---------------------------|--------|--------|------|------------------|------------------------------------|

| High Level Input Voltage  | VIH    | 2.0    |      | V                |                                    |

| Low Level Input Voltage   | VIL    |        | 0.8  | V                |                                    |

| High Level Output Voltage | VOH    | 0.9VDD |      | V                | IOH = -0.2mA                       |

| Low Level Output Voltage  | VOL    |        | 0.4  | v                | IOL=1mA (SDA-pin, TXFAULT-pin)     |

|                           |        |        |      | _                | IOL=0.2mA (Excluding SDA, TXFAULT) |

| Input Leakage Current 1   | IL1    |        | 10   | $\mu \mathbf{A}$ | Excluding WP-pin                   |

| Input Leakage Current 2   | IL2    |        | 350  | $\mu \mathbf{A}$ | WP-pin                             |

(3) Digital Input / Output Pin DC Characteristics

## <MS0290-E-01>

#### ASAHI KASEI

Symbol

tSCL

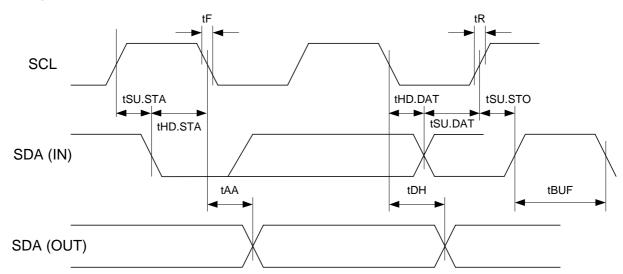

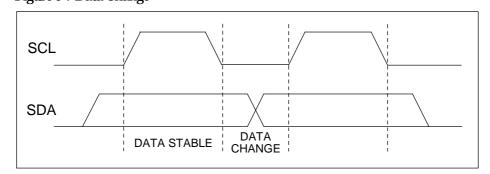

## (4) Digital Input / Output Pin AC Characteristics (Serial Interface)

Parameter

**Clock Frequency, SCL**

| Clock Pulse Width Low          | 4.7                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ <b>S</b>                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                                                                                                                                                                            |                                                                                                                                                                                                                                      | μυ                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |

| Clock Pulse Width High         | 4.0                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Noise Suppression Time         |                                                                                                                                                                                                            | 100                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |

| Clock Low to Data Out Valid    | 0.1                                                                                                                                                                                                        | 4.5                                                                                                                                                                                                                                  | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

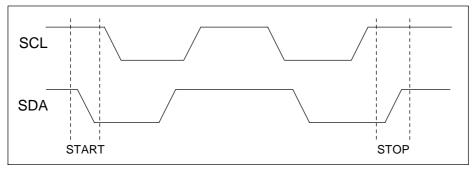

| Time before a New Transmission | 4.7                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Start Hold Time                | 4.0                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Start Setup Time               | 4.7                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Data Hold Time                 | 0                                                                                                                                                                                                          |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Data Setup Time                | 200                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |

| Input Rise Time                |                                                                                                                                                                                                            | 1.0                                                                                                                                                                                                                                  | $\mu$ S                                                                                                                                                                                                                    | [*]                                                                                                                                                                                                                                                                                                                                                                       |

| Input Fall Time                |                                                                                                                                                                                                            | 0.3                                                                                                                                                                                                                                  | $\mu$ S                                                                                                                                                                                                                    | [*]                                                                                                                                                                                                                                                                                                                                                                       |

| Stop Setup Time                | 4.0                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | $\mu$ S                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                           |

| Data Out Hold Time             | 100                                                                                                                                                                                                        |                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |

| Write Cycle Time               |                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                   | ms                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                           |

| -<br>-<br>-<br>-               | Noise Suppression TimeClock Low to Data Out ValidTime before a New TransmissionStart Hold TimeStart Setup TimeData Hold TimeData Setup TimeInput Rise TimeInput Fall TimeStop Setup TimeData Out Hold Time | Noise Suppression TimeClock Low to Data Out Valid0.1Time before a New Transmission4.7Start Hold Time4.0Start Setup Time4.7Data Hold Time0Data Setup Time200Input Rise Time1Stop Setup Time4.0Stop Setup Time4.0Data Out Hold Time100 | Noise Suppression Time100Clock Low to Data Out Valid0.14.5Time before a New Transmission4.7100Start Hold Time4.0100Start Setup Time4.7100Data Hold Time0100Data Setup Time2001.0Input Rise Time1.00.3Stop Setup Time4.0100 | Noise Suppression Time100nsClock Low to Data Out Valid0.14.5 $\mu$ sTime before a New Transmission4.7 $\mu$ sStart Hold Time4.0 $\mu$ sStart Setup Time4.7 $\mu$ sData Hold Time0 $\mu$ sData Setup Time200nsInput Rise Time1.0 $\mu$ sStop Setup Time4.0 $\mu$ sData Out Hold Time0.3 $\mu$ sStop Setup Time4.0 $\mu$ sStop Setup Time1.0 $\mu$ sData Out Hold Time100ns |

Min.

Max.

100

Unit

kHz

Note

#### (5) I-DAC1 Characteristics

| Item                                 | Condition  | Min. | Тур. | Max. | Unit             | Note                             |

|--------------------------------------|------------|------|------|------|------------------|----------------------------------|

| Resolution                           |            |      | 8    |      | bit              | Straight Binary                  |

| Maximum Output<br>Current 1 (Source) | IOUT1=1.3V | 9.4  | 10.2 | 11.0 | mA               | Input Code=FFh<br>RE_DAC1_GAIN=1 |

| Maximum Output<br>Current 2 (Source) | IOUT1=1.3V | 0.94 | 1.02 | 1.10 | mA               | Input Code=FFh<br>RE_DAC1_GAIN=0 |

| Current Supply at<br>Shutdown        | IOUT1=VSS  |      |      | 10   | $\mu \mathbf{A}$ | RE_MODV_SEL=0<br>TXDIS="H" [*]   |

| 1 LSB Current Step 1                 | IOUT1=1.3V |      | 40.0 |      | $\mu \mathbf{A}$ | RE_DAC1_GAIN=1                   |

| 1 LSB Current Step 2                 | IOUT1=1.3V |      | 4.0  |      | $\mu \mathbf{A}$ | RE_DAC1_GAIN=0                   |

| DNL                                  | IOUT1=1.3V | - 1  |      | +1   | LSB              | Input Code=10h~FFh               |

| INL                                  | IOUT1=1.3V | - 2  |      | +2   | LSB              | Input Code=10h~FFh               |

[\*] At RE\_SFP\_SET="0", a logical sum of TXFAULT output and TXDIS-pin input becomes a disable request. Refer to Table 7-1.

#### (6) I-DAC2 Characteristics

| Item                               | Condition      | Min. | Тур. | Max. | Unit             | Note                             |

|------------------------------------|----------------|------|------|------|------------------|----------------------------------|

| Resolution                         |                |      | 8    |      | bit              | Straight Binary                  |

| Maximum Output<br>Current 1 (Sink) | IOUT2=VDD-1.7V | 78.2 | 85.0 | 91.8 | mA               | Input Code=FFh<br>RE_DAC2_GAIN=1 |

| Maximum Output<br>Current 2 (Sink) | IOUT2=VDD-1.7V | 39.1 | 42.5 | 45.9 | mA               | Input Code=FFh<br>RE_DAC2_GAIN=0 |

| Current Supply at<br>Shutdown      | IOUT2=VDD      |      |      | 100  | $\mu \mathbf{A}$ | TXDIS="H" [*]                    |

| 1 LSB Current Step 1               | IOUT2=VDD-1.7V |      | 333  |      | $\mu \mathbf{A}$ | RE_DAC2_GAIN=1                   |

| 1 LSB Current Step 2               | IOUT2=VDD-1.7V |      | 167  |      | $\mu \mathbf{A}$ | RE_DAC2_GAIN=0                   |

| DNL                                | IOUT2=VDD-1.7V | - 1  |      | +1   | LSB              | Input Code=10h~FFh               |

| INL                                | IOUT2=VDD-1.7V | - 2  |      | +2   | LSB              | Input Code=10h~FFh               |

[\*] At RE\_SFP\_SET="0", a logical sum of TXFAULT output and TXDIS-pin input becomes a disable request. Refer to Table 7-1.

#### (7) V-DAC3 Characteristics

| Item                          | Condition             | Min. | Тур. | Max. | Unit | Note                             |

|-------------------------------|-----------------------|------|------|------|------|----------------------------------|

| Resolution                    |                       |      | 8    |      | bit  | Straight Binary                  |

| Maximum Output<br>Voltage 1   | 10k $\Omega$ (to VSS) | 1.11 | 1.20 | 1.29 | V    | Input Code=FFh<br>RE_DAC3_GAIN=1 |

| Maximum Output<br>Voltage 2   | 10k $\Omega$ (to VSS) | 2.03 | 2.20 | 2.37 | V    | Input Code=FFh<br>RE_DAC3_GAIN=0 |

| Minimum Output<br>Voltage     | 10k $\Omega$ (to VDD) |      |      | 0.2  | V    | Input Code=00h                   |

| Voltage Supply at<br>Shutdown | 10k $\Omega$ (to VDD) |      |      | 0.2  | V    | RE_MODV_SEL=1<br>TXDIS="H" [*]   |

| 1 LSB Voltage Step 1          | 10k $\Omega$ (to VSS) |      | 4.7  |      | mV   | RE_DAC3_GAIN=1                   |

| 1 LSB Voltage Step 2          | 10k $\Omega$ (to VSS) |      | 8.6  |      | mV   | RE_DAC3_GAIN=0                   |

| DNL                           | 10k $\Omega$ (to VSS) | - 1  |      | + 1  | LSB  | Input Code=20h~FFh               |

| INL                           | 10k $\Omega$ (to VSS) | - 2  |      | +2   | LSB  | Input Code=20h~FFh               |

[\*] At RE\_SFP\_SET="0", a logical sum of TXFAULT output and TXDIS-pin input becomes a disable request. Refer to Table 7-1.

## (8) Current Monitor (BIASMON)

| Item                                 | Condition    | Min. | Тур.  | Max. | Unit | Note                              |  |  |  |

|--------------------------------------|--------------|------|-------|------|------|-----------------------------------|--|--|--|

| BIASMON Current                      | BIASMON=1.3V |      | 0.012 |      | Time | Based on I-DAC2<br>Input Code=FFh |  |  |  |

| Maximum Output<br>Current 1 (Source) | BIASMON=1.3V | 0.94 | 1.02  | 1.10 | mA   | Input Code=FFh<br>RE_DAC2_GAIN=1  |  |  |  |

| Maximum Output<br>Current 2 (Source) | BIASMON=1.3V | 0.47 | 0.51  | 0.55 | mA   | Input Code=FFh<br>RE_DAC2_GAIN=0  |  |  |  |

## (9) PDGAIN

| Item              | Condition    | Min.  | Тур. | Max.  | Unit | Note |

|-------------------|--------------|-------|------|-------|------|------|

| PDIN Input Range  | PDMON=1V±10% | 0.08  |      | 2.5   | V    |      |

| PDGAIN Gain Error | PDIN→PDMON   | - 0.5 |      | + 0.5 | dB   |      |

## (10) DAC\_APC

| Item                   | Condition            | Min.  | Тур.  | Max.  | Unit | Note |

|------------------------|----------------------|-------|-------|-------|------|------|

| Maximum Output Voltage | Test mode, PDMON-pin | 1.135 | 1.195 | 1.255 | V    |      |

| Minimum Output Voltage | Test mode, PDMON-pin | 0.752 | 0.792 | 0.832 |      |      |

| DNL                    | Test mode, PDMON-pin | - 1   |       | +1    | LSB  |      |

#### (11) BIASGEN

| Item             | Condition         | Min. | Тур. | Max. | Unit | Note |

|------------------|-------------------|------|------|------|------|------|

| BIAS-pin Voltage | $12k\Omega\pm1\%$ |      | 1.2  |      | V    |      |

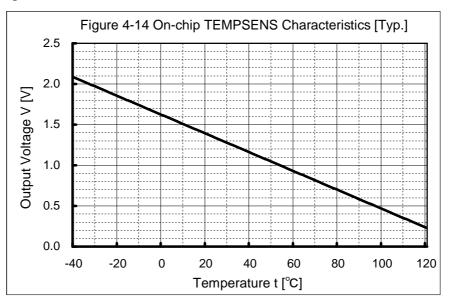

#### (12) Temperature Sensor

| Item                     | Condition           | Min.    | Тур.    | Max.    | Unit  | Note |

|--------------------------|---------------------|---------|---------|---------|-------|------|

| Voltage Slope            | TEMPMON-pin Voltage | - 12.14 | - 11.56 | - 10.98 | mV/°C | [*]  |

| Offset Adjustment Target | <b>Ta=35</b> ℃      |         | 1.215   |         | V     |      |

[\*] This parameter is characterized and is not 100% tested.

#### (13) ADC

| Item                  | Condition | Min. | Тур. | Max. | Unit | Note            |

|-----------------------|-----------|------|------|------|------|-----------------|

| Resolution            |           |      | 8    |      | bit  | Straight Binary |

| Maximum Input Voltage |           | 2.09 | 2.20 | 2.31 | V    | $\pm$ 5%        |

| Minimum Input Voltage |           |      | 0    |      | mV   |                 |

| DNL                   |           | - 1  |      | +1   | LSB  |                 |

| INL                   |           | - 2  |      | +2   | LSB  |                 |

#### (14) Power On Reset

| Item           | Condition | Min. | Тур. | Max. | Unit | Note |

|----------------|-----------|------|------|------|------|------|

| Detect Voltage |           | 2.3  | 2.5  | 2.7  | V    |      |

(15) On-chip Oscillator

| Item            | Condition | Min. | Тур.  | Max. | Unit | Note |

|-----------------|-----------|------|-------|------|------|------|

| Clock Frequency | Test mode |      | 8.192 |      | MHz  |      |

## (16) OPTALM

| Item                 | Condition               | Min.  | Тур. | Max.  | Unit | Note |

|----------------------|-------------------------|-------|------|-------|------|------|

|                      | 1/3 setting, PDGAIN=0dB | 1/3.2 | 1/3  | 1/2.8 | Time |      |

| <b>OPTALM Detect</b> | 1/4 setting, PDGAIN=0dB | 1/4.3 | 1/4  | 1/3.7 | Time |      |

| Level                | 1/6 setting, PDGAIN=0dB | 1/6.4 | 1/6  | 1/5.6 | Time |      |

|                      | 1/7 setting, PDGAIN=0dB | 1/7.5 | 1/7  | 1/6.5 | Time |      |

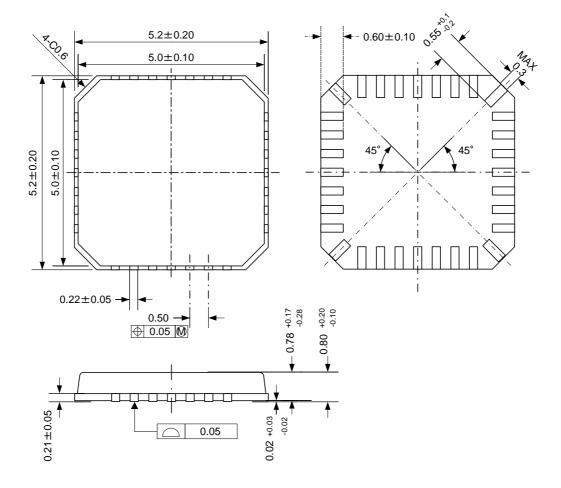

(3) Package Outline Dimension

## VI. CIRCUIT DESCRIPTION

#### 1. Operational Description Notation

In order to distinguish various pre-set parameter sources from EEPROM, Registers or Device pins, "Identifier – Main name "notation is used in the AK2572 circuit description as shown in Table 1-1. For ease of operational description, internal signals are sometimes defined which are all expressed in small letters.

|                                          | Identifier | Main name                                     | Remark                                              | Example      |

|------------------------------------------|------------|-----------------------------------------------|-----------------------------------------------------|--------------|

| Register                                 | R_         | REGISTER name<br>(All Capital)                | Indicating Register                                 | R_DAC2       |

| EEPROM                                   | E_         | EEPROM name<br>(All Capital)                  | Indicating EEPROM                                   | E_BIAS_TC    |

| Either or Both Register<br>or/and EEPROM | RE_        | REGISTER name<br>EEPROM name<br>(All Capital) | Indicating either or both<br>Register or/and EEPROM | RE_DAC3_GAIN |

| BLOCK                                    |            | BLOCK name<br>(All Capital)                   |                                                     | I-DAC1       |

| Internal node                            |            | signal name<br>(All small letter)             |                                                     | vpd          |

Table 1-1 Definition of Terms

Identification words are assigned to the name of Register / EEPROM as shown in Table 1-2 so that each function can be easily assumed by each name.

| Classification | Suffix | Contents                                          | Example        |

|----------------|--------|---------------------------------------------------|----------------|

| Identification | _SET   | Functional setting                                | RE_APC_FF_SET  |

| suffix         | _SEL   | Functional selection                              | E_MODV_SEL     |

|                | _TC    | Temperature compensation value                    | E_MOD_TC       |

|                | _WIN   | Window width setting by ALM set                   | RE_TEMP_WIN    |

|                | _TRGT  | Target value                                      | RE_APC_TRGT    |

| Functional     | APC    | APC related, common for I-DAC1, I-DAC2 and V-DAC3 | RE_APC_FF_SET  |

| identification | DAC    | I-DAC, V-DAC related                              | E_DAC_SET      |

| word           | BIAS   | Bias current (I-DAC2) related                     | R_BIAS_FF      |

|                | MOD    | MOD current (I-DAC1, V-DAC3) related              | E_MOD_TC       |

|                | EXTRA  | EXTRA DAC (DAC not set to MOD) related            | R_EXTRA        |

|                | TEMP   | Temperature sensor related                        | R_TEMP         |

|                | PWR    | Power leveling function related                   | R_PWR_SEL      |

|                | ALM    | Alarm related                                     | R_TEMPALM_SET  |

|                | FF     | FeedForward function                              | RE_APC_FF_SET  |

|                | FB     | FeedBack function                                 | RE_APC_FB_SET  |

|                | FBRT   | FB dividing                                       | R_MOD_FBRT     |

|                | TIMER  | Timer related                                     | R_TIMER_OPTALM |

|                | GAIN   | Gain adjust                                       | E_DAC1_GAIN    |

|                | BURST  | Burst mode support function related               | E_BURST_ALM    |

|                | ST     | Status signals                                    | R_TXFLT_ST     |

|                | POL    | Signal polarity                                   | E_EXTALM1_POL  |

Table 1-2 Identification Word Classification

< Note > Numeric values in the circuit description of the AK2572 are expressed in Binary, Decimal or Hexadecimal. In order to identify the differences, setting values in Hexadecimal are expressed with a small character "h" suffix.

## 2. Operation Setting

The AK2572 can operate following functions as shown in Table 2-1 by EEPROM / Register setting. For further details, please refer to the circuit description at the next page and thereafter.

| Table 2-1 AR2572 Operation |                                               | Set-up |         |              | Related setting                                   |

|----------------------------|-----------------------------------------------|--------|---------|--------------|---------------------------------------------------|

| RE BURST SET               | 0                                             | Set up | 1       |              | Instanta Settilles                                |

| RE_SFP_SET [*3]            | 0 1                                           |        | 1       |              |                                                   |

| RE_PWR_LVL1_SET [*3]       | 0                                             | 1      | 0 1     |              |                                                   |

| RE PWR LVL2 SET            | 0                                             |        | 1       | 0            |                                                   |

| RE APC FF SET              | 00 ~ 11 (0 ~                                  | 3)     | 11 (3)  |              |                                                   |

| RE APC FB SET              | 00~11 (0~                                     |        | 0       |              |                                                   |

| RE OPTALM SET              | 0/1                                           | -,     | 0       |              |                                                   |

| RE_CURRALM_SET             | 0/1                                           |        | 0       |              |                                                   |

| Continuous mode            | 0                                             |        | ×       |              |                                                   |

| Burst mode                 | ×                                             |        | 0       |              |                                                   |

| SFP_MSA support            | 0                                             | ×      | ×       |              |                                                   |

| Shutdown request           | Logical sum (ORed)<br>of TXFAULT and<br>TXDIS | TXDIS  | TXDI    | S            |                                                   |

| Power leveling [1]         | ×                                             |        | ×       | 0            | MOD_CTRL-pin<br>E_MOD_TC[1]<br>E_MOD_TC[2]        |

| EXTALM2<br>/MOD_CTRL-pin   | EXTALM                                        | 2      | EXTALM2 | MOD<br>_CTRL |                                                   |

| Power leveling [2]         | Х                                             |        | 0       | ×            | RE_PWR_SEL<br>E_BIAS_TC[0]~[3]<br>E_MOD_TC[0]~[3] |

| APC_FF function            | □ [* <b>1</b> ]                               |        | ○ [*2   | 2]           |                                                   |

| APC_FB function            | <br>[*1]                                      |        | × [*2]  |              |                                                   |

| OPTALM                     | □ [*1]                                        |        | × [*2   | 2]           | RE_OPTALM<br>RE_TIMER_OPTALM                      |

| CURRALM                    | □ [*1]                                        |        | × [*2   | 2]           | E_CURRALM_BIAS_TC<br>E_CURRALM_MOD_TC             |

Table 2-1 AK2572 Operation Setting

[\*1] These functions are determined by the corresponding EEPROM / Register setting. Therefore the operations of " $\Box$ " depend on the user's setting.

[\*2] In Burst mode setting (RE\_BURST\_SET="1", RE\_SFP\_SET="1"), it is assumed that only APC\_FF function is used and no APC\_FB function is used (Monitor PD, CURRALM and OPTALM are not used). [\*3] Setting of RE\_SFP\_SET="0" and R\_PWR\_LVL1\_SET="1" is prohibited.

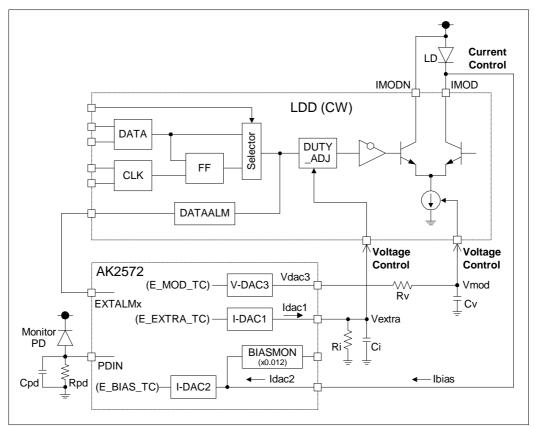

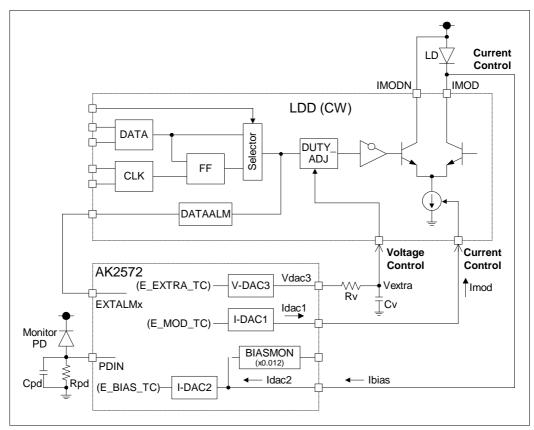

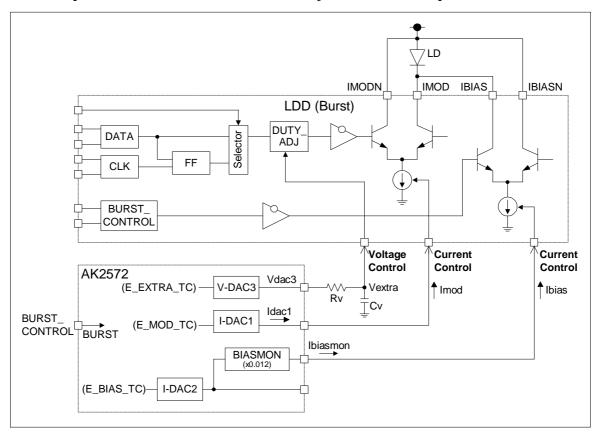

## 3. I-DAC, V-DAC Functional Part

The AK2572 equips Current source type I-DAC1 (Max. sourcing current=10.2 mA [Typ.]) and Voltage output type V-DAC3 (Max. output voltage=2.2 V [Typ.]) for the LD modulation current setting, and Current sink type I-DAC2 (Max. sink current=85.0 mA [Typ.]) for the bias current setting. Selection of enable / disable each DAC is set by RE\_DAC\_SET. Output current of I-DAC1 (Max. value=10.2 mA / 1.02 mA [Typ.]) and I-DAC2 (Max. value=85.0 mA / 42.5 mA [Typ.]), and output voltage of V-DAC3 (Max. value=2.2 V / 1.2 V [Typ.]) can be switched by gain setting. This gain switching allows to lower current consumption and to improve the accuracy per 1 LSB. In Tables 3-1 ~ 3-3, the characteristics of I-DAC2, I-DAC1 and V-DAC3 are shown.

I-DAC2 directly sets the LD bias current. A current multiplied by a factor of 0.012 [Typ.] of I-DAC2 set value is output (Current source) on BIASMON-pin.

| RE_DAC2_GAIN | Gain | Max. output current (Code=FFh)[Typ] | Range [Typ]              | Current/step [Typ]    |

|--------------|------|-------------------------------------|--------------------------|-----------------------|

| 1            | 1    | 85.0 mA                             | $0 \sim 85.0  mA$        | <b>333</b> μ <b>A</b> |

| 0            | 1/2  | 42.5 mA                             | $0 \sim 42.5 \text{ mA}$ | <b>167</b> μ <b>A</b> |

Table 3-1 I-DAC2 characteristics (I-DAC2 is set "Enabled" / "Disabled" by RE\_DAC\_SET [1] = "1" / "0")

[Note] I-DAC2 characteristics : Resolution = 8 bits, DNL =  $\pm 1$  LSB (DAC code = 10h ~ FFh)

Output current variation at Maximum DAC code (FFh)=Typ. $\pm 8\%$

Temperature compensation data (Retained in EEPROM), which are set for I-DAC1 and V-DAC3, can be selected by RE\_MODV\_SEL setting as shown in Table 3-4.

When E\_MOD\_TC (128 address locations) is assigned as the setting data, I-DAC1(RE\_MODV\_SEL="0") generates a reference current of the modulation current to external Laser Diode Driver (LDD), and V-DAC3 (RE\_MODV\_SEL="1") generates a reference voltage of the Modulation current to external LDD. A voltage driver type LDD can also be adopted by converting an I-DAC1 output current to a voltage by external resistors or by using V-DAC3 output voltage. When E\_EXTRA\_TC (32 address locations) is assigned as the setting data, I-DAC1 output (RE\_MODV\_SEL="1") or V-DAC3 output (RE\_MODV\_SEL="0") can be used as APD control voltage or LDD reference voltage etc.. When temperature compensation by E\_EXTRA\_TC is not required, same data should be written at all address locations.

Table 3-2 I-DAC1 characteristics (I-DAC1 is set "Enabled" / "Disabled" by RE\_DAC\_SET [0]="1" / "0")

| RE_DAC1_GAIN | Gain | Max. output current (Code=FFh)[Typ] | Range [Typ]              | Current/step[Typ]    |

|--------------|------|-------------------------------------|--------------------------|----------------------|

| 1            | 1    | 10.2 mA                             | $0 \sim 10.2 \text{ mA}$ | <b>40</b> μ <b>A</b> |

| 0            | 1/10 | 1.02 mA                             | $0 \sim 1.02 \text{ mA}$ | <b>4</b> μ <b>A</b>  |

[Note] I-DAC1 characteristics : Resolution=8 bits, DNL= $\pm 1$  LSB (DAC code=10h ~ FFh) Output current variation at Maximum DAC code (FFh)=Typ. $\pm 8$  %

Table 3-3 V-DAC3 characteristics (V-DAC3 is set "Enabled" / "Disabled" by RE\_DAC\_SET [2]="1" / "0")

| RE_DAC3_GAIN | Gain    | Max. output voltage (Code=FFh)[Typ] | Range [Typ]            | Voltage/step[Typ] |

|--------------|---------|-------------------------------------|------------------------|-------------------|

| 1            | 1.2/2.2 | 1.2 V                               | $0 \sim 1.2 \text{ V}$ | 4.7 mV            |

| 0            | 1       | 2.2 V                               | $0 \sim 2.2 \ V$       | 8.6 mV            |

[Note] V-DAC3characteristics: Resolution=8 bits, DNL=±1 LSB (DAC code=20h ~ FFh) Output voltage variation at Maximum DAC code (FFh)=Typ.±8 %

Table 3-4 RE\_MODV\_SEL setting

| RE_MODV_SEL | I-DAC1     | V-DAC3     |

|-------------|------------|------------|

| 0           | E_MOD_TC   | E_EXTRA_TC |

| 1           | E_EXTRA_TC | E_MOD_TC   |

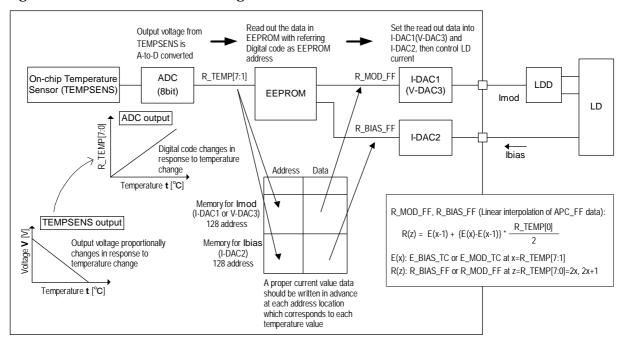

[Note] Although E\_MOD\_TC has 128 address locations and E\_EXTRA\_TC has 32 address locations, temperature resolution of each temperature compensation data is 0.75  $^{\circ}$ C [typ.] because of the temperature compensation data is derived from a linear interpolation method (Refer to Section 4.1).

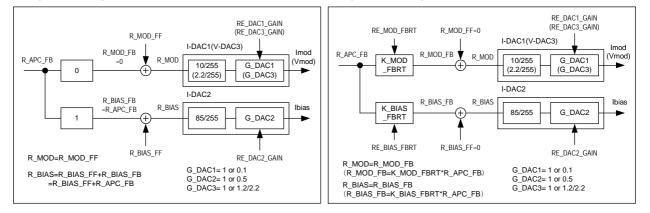

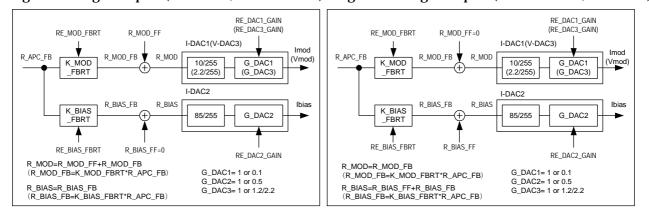

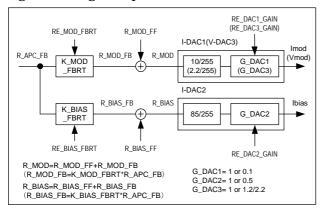

## 4. APC Functional Part